光刻是半導體行業的核心技術。自仙童半導體公司的羅伯特諾伊斯在1960年發明單片集成電路以來,光刻技術一直是主要的光刻技術。

本質上,陰影掩模(s*ow mask)用來協助一種稱爲光刻膠的光敏材料進行圖案化,從而能夠進行圖案化沉積和蝕刻工藝。而光刻工藝的*終解決方案是由所用光源的波長決定的。

在開發更短波長的光刻源方面取得了進步。這使得以摩爾定律爲特征的電路密度不斷增加。曆史上使用汞放電燈,例如 365 nm i-Line,但*近使用 248 nm 的 KrF 或 193 nm 的 ArF 準分子激光器成爲*光源。當使用液體浸沒技術時,ArF 激光器獲得的*終分辨率約爲 50 nm,其中透鏡和半導體晶片浸入水中,水中的折射率高于空氣。

過去二十年見證了193 nm以下波長光刻技術的發展。在使用 F2 準分子激光器開發基于 157 納米的光刻技術方面付出了一些努力,但主要關注點是使用 13.5 納米軟 X 射線作爲光源的極紫外 (EUV) 光刻技術。

荷蘭公司 ASML 在 EUV 技術的開發中發揮了主導作用,他們的工具集現在被包括英特爾、三星和台積電在内的主要* CMOS 代工廠用于生産。

光刻方法的實踐

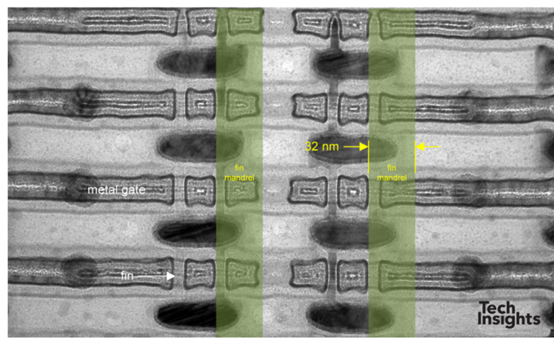

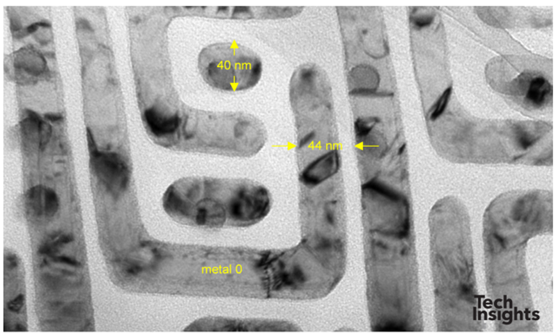

應用許多光刻方法來産生單芯片設計。TechInsights *近對三星 5LPE 工藝進行了詳細分析。圖 1 顯示了器件 CPU 邏輯區域中栅極和鳍片布局的平面圖 TEM 圖像。

圖 1:Samsung 5LPE Gate and Fin Layout

自對準四重圖案化 (SAQP) 幾乎可以肯定用于對鳍進行圖案化。圖像注釋中顯示了 fin mandrels的大緻位置,該位置将使用 ArF 193 nm 浸入式 (ArF 193i) 光刻進行圖案化。然後将通過在mandrel上創建 sidewall spacers來形成*終的 fin pattern。mandrel将具有 108 nm 的間距(pitch)。然後移除mandrel,然後使用*個側壁間隔物( sidewall spacer)圖案來創建第二組側壁間隔物,*終的鳍間距爲 27 nm。

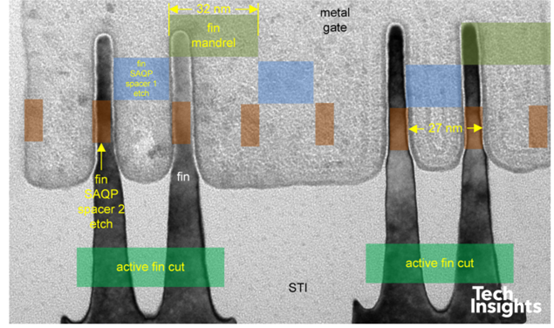

兩組側壁間隔物的大緻位置和尺寸如圖 2所示,這是一張橫截面 TEM 圖像,顯示邏輯區域中三星 5LPE 工藝的 27 nm 間距鳍結構.

圖 2:Samsung 5LPE Fin Cross Section

然後将使用有源鳍(active fin)切割掩模去除不需要的鳍并用淺溝槽隔離 (STI:shallow trench isolation) 替換它們。圖 1中所示的金屬栅極很可能是使用自對準雙圖案化 (SADP) 技術形成的,其中mandrel上的側壁間隔物直接用于圖案化多晶矽栅極,後來被金屬栅極取代。

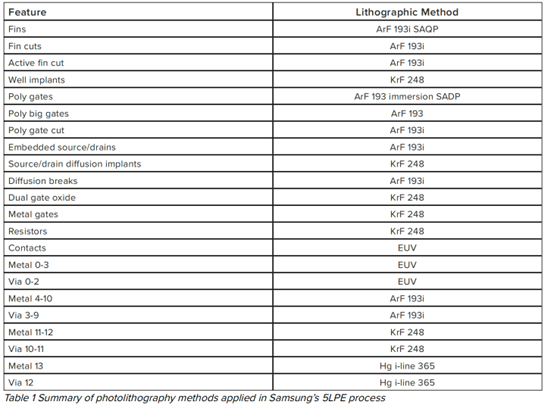

目前正在生産的*半導體器件的尺寸明顯小于使用 ArF 浸沒式光刻技術可獲得的約 50 nm *小半間距。這需要開發越來越複雜的工藝技術方案。例如,根據*近的 TechInsights 分析結果,三星 5 納米 LPE 工藝使用了多種*的光刻方法,包括 EUV,如表 1 所示。

表 1

SAQP光刻技術可以産生非常精細的間距特征;但是,它僅限于創建沿單個方向定向的單軸結構( uniaxial structures)。線路末端需要特殊切割( Special cut)的掩模,以防止相鄰線路之間短路。EUV 光刻沒有這些限制,但成本較高。

圖 3 顯示了三星 5LPE 設備的 CPU 邏輯區域中metal 0 布局的平面圖 TEM 顯微照片。觀察到的*小金屬間距約爲 44 nm。此外,布局包括在兩個正交方向上定向的線。這在使用 SADP 或 SAQP ArF 193i 光刻方法時通常是不可能的。

圖 3:Samsung 5LP Metal 0 Layout

納米壓印光刻和直接自組裝光刻

EUV 設備和工藝非常複雜和昂貴,因此業界一直在研究替代品。三個主要競争者是:

1. 納米壓印光刻 (NIL:Nano-Imprint Lithography)

2. 直接自組裝 (DSA:Direct Self-Assembly) 光刻

3. 電子束光刻 (EBL:Electron Beam Lithography)

其中,EBL 提供非常高的空間分辨率(優于 10 nm),但配置和執行速度較慢,本文将不作進一步考慮。EBL 确實有商業應用,但不是在大批量*節點制造中。

納米壓印光刻技術*早由明尼蘇達大學的Stephen Chu 提出。該技術基于聚甲基丙烯酸甲酯 (PMMA) 的壓縮成型。Chu 和他的合著者在 1996 年發表在《科學》雜志上的一篇論文中報告了 25 nm 分辨率的圖案化。他們于 1995 年發布了開創性* US577290*。NIL 技術于 2003 年被添加到 ITRS 路線圖中,該領域一直是持續研究和開發的領域。佳能是全球主要的光刻設備供應商之一,并且他們現在提供 NIL 産品線,東芝是他們的早期客戶之一,建議的應用是 NAND 閃存生産。

直接自組裝光刻取決于嵌段共聚物(block-copolymers)在預圖案化基闆上的直接定向。該技術類似于 SADP 和 SAQP,因爲使用較粗的間距模闆(coarser pitch template)來創建較細的間距結構( finer pitch structure)。DSA 技術于 1990 年代*提出,并于 2007 年成爲 ITRS 路線圖的一部分。DSA 的主要支持者是 IMEC 的一個研究小組。2021 年,他們展示了使用 DSA 形成 18 納米間距線圖案。據我們所知,直接自組裝尚未被任何主要半導體代工廠用于大批量生産。在過去的二十年裏,這項技術進行了大量的研發和*活動,但還沒有商業用途。

*光刻的創新*

TechInsights與 Cipher 合作,一直在探索*光刻市場的創新。目前,基于光學光刻的技術主導着半導體市場,其中 ArF 193i 是用于圖案化細間距特征的主要方法。基于 EUV 的光刻開始出現在**的 CMOS 技術中,例如上一節中讨論的三星 5LPE。

不幸的是,EUV 方法非常昂貴,并且可能存在與 ASML 交付 EUV 硬件相關的供應鏈問題。我們預計該行業将積極尋求替代方案。Cipher 一直與 TechInsights 合作開發*分類器,可用于監控特定領域的創新步伐,例如 EUV、NIL 和 DSA 光刻。

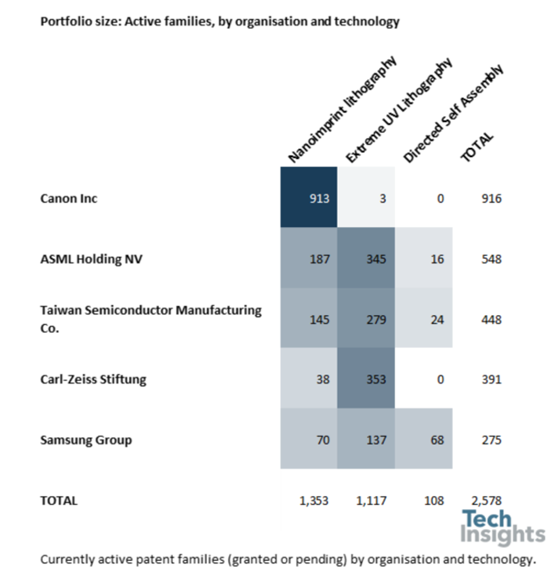

Cipher *分類器使 TechInsights 能夠繪制出 EUV、NIL 和 DSA *光刻*的概況。圖 4 顯示了按技術排名前 5 位的*組織的表格。

圖 4:Top 5 Companies by NIL, EUV and DSA Patent Holdings

表格顯示:

• 佳能顯然對 NIL 技術寄予厚望;

• ASML 對 EUV 的投資*多,但也積極參與 NIL 和 DSA 研究;

• 從*光刻研發的角度來看,台積電顯然是*的代工廠。他們是對 EUV 投資*多,但在 NIL 和 DSA 方面也很活躍;

• 三星排在第五位,也在兩面下注,盡管他們的*活動水平遠低于台積電;

• Karl-Zeiss 排在第四位,他們作爲光刻供應商的主要關注點是 EUV 也就不足爲奇了;

該表未顯示包括GlobalFoundries、IBM 和 Intel 在内的北美主要組織,它們的排名更靠後,分别位于第 16 位、第 17 位和第 32 位。

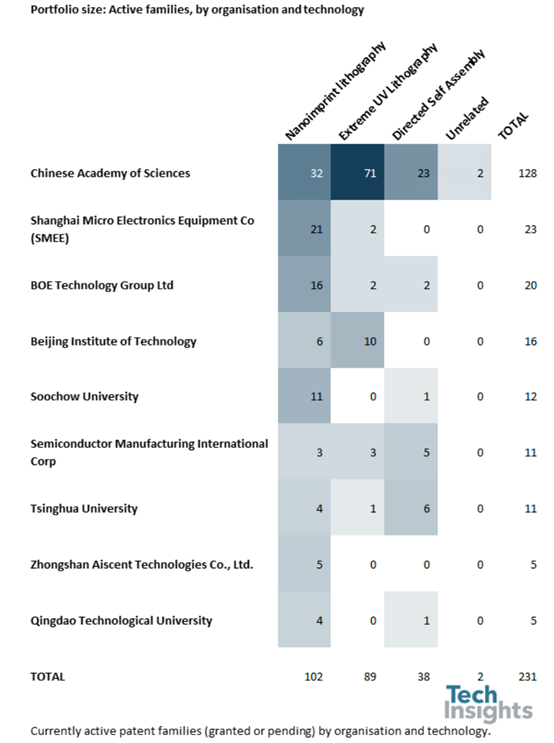

圖 5 根據 Cipher *分類器獲得的結果,将中國排名前 10 位實體的*格局與世界其他地區進行比較,按組織和光刻技術類型列出了當前活躍*家族的數量。

圖 5:Counts of Current Active Patent Families by Organization and Technology for China

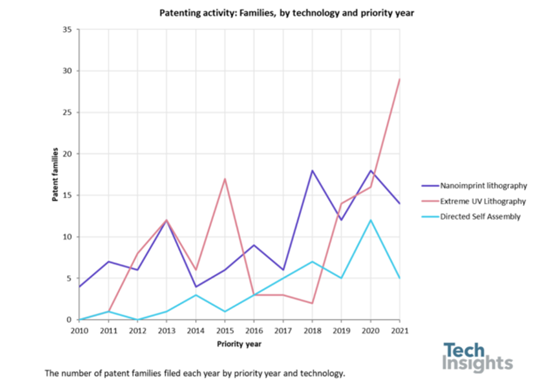

圖 6顯示了按年份和*光刻技術提交的*族數量僅供中國公司使用的空間。*總數相當少,但有持續的EUV、DSA 和 NIL 這三個技術領域的*活動呈上升趨勢。

圖 6:Number of Patent Families Filed by Year and Technology for China

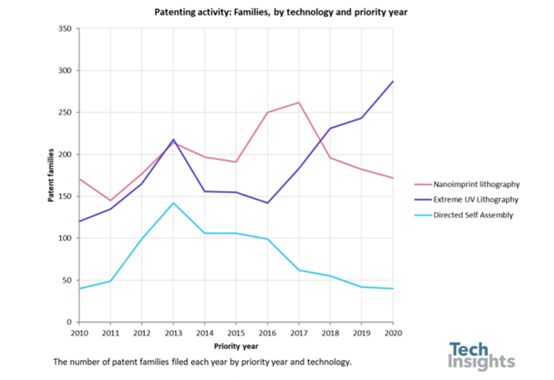

相比之下,圖 7顯示了世界其他地區(不包括中國)在*光刻領域按年份和技術提交的*族數量。

圖 7:Number of Patent Families Filed by Year and Technology for Rest of World

當然,世界其他地區的*數量要多于中國。數據顯示 EUV *活動呈持續上升趨勢;然而,大約在 2013 年之後,DSA *活動和 NIL 技術*活動在大約 2018 年之後有所下降。這也許并不奇怪,因爲 ASML EUV 技術現已商用,從而減少了尋找替代品的動力。

結論

*的光刻技術對于摩爾定律擴展的延續*關重要。該行業目前正在押注EUV,輔以*的 193i 技術,如 SADP 和 SAQP,将繼續縮小到上面讨論的 5 納米技術以下。不幸的是,EUV 取決于使用極其複雜和昂貴的設備,因此該行業繼續尋找替代品,例如作爲 NIL 或 DSA,這可能會提供一條替代途徑。

審核編輯 :李倩